微电子所在低功耗模数转换器研究领域取得进展

作者: 2017年08月25日 来源: 浏览量:

字号:T | T

近日,中国科学院微电子研究所智能感知研发中心研究员樊晓华团队研发出一款13位50MS/s的混合型模数转换器(ADC),品质因数(FOM)达到国际领先水平。 该款ADC采用了基于量程辅助、逐次逼近、流水线等技术的混合

近日,中国科学院微电子研究所智能感知研发中心研究员樊晓华团队研发出一款13位50MS/s的混合型模数转换器(ADC),品质因数(FOM)达到国际领先水平。

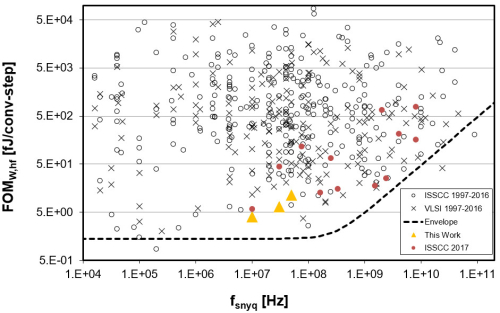

该款ADC采用了基于量程辅助、逐次逼近、流水线等技术的混合型架构,在国际上首次提出高增益(32倍)PVT不敏感的时间域放大器,显著降低了ADC的功耗及校准算法复杂度,提出了量程辅助的悬空电容阵列开关算法及预开窗异步控制逻辑,提高了ADC的转换速率。该ADC在130nm CMOS工艺下流片成功,有效核心面积0.22mm2。测试结果表明,在1.2V供电、50MS/s转换速率下,输入信号为2MHz时,ADC的信噪失真比(SNDR)达71.6dB,无杂散动态范围(SFDR)达84.6dB。该ADC支持可变电源电压与转换速率,当电源电压从0.8V变化到1.2V时,ADC的转换速率为10-50MS/s,Walden FOM值为4.0-11.3 fJ/conversion-step。

此项工作主要由樊晓华、博士张明磊完成,得到美国德克萨斯农工大学教授Edgar Sánchez-Sinencio的支持。该款ADC可满足当前高速发展的片上集成系统对低功耗、高速度以及高精度等特性的严格要求,可运用于多种便携式通信系统的应用场景。相关研究成果已被IEEE Journal of Solid State Circuits接收。

图1.ADC芯片照片

图2.不同模式下SFDR/SNDR随输入频率的变化

图3.FOM值与国际顶级会议(ISSCC/VLSI)的比较

全球化工设备网(http://www.chemsb.com )友情提醒,转载请务必注明来源:全球化工设备网!违者必究.

标签:

相关资讯

免责声明:1、本文系本网编辑转载或者作者自行发布,本网发布文章的目的在于传递更多信息给访问者,并不代表本网赞同其观点,同时本网亦不对文章内容的真实性负责。

2、如涉及作品内容、版权和其它问题,请在30日内与本网联系,我们将在第一时间作出适当处理!有关作品版权事宜请联系:+86-571-88970062

2、如涉及作品内容、版权和其它问题,请在30日内与本网联系,我们将在第一时间作出适当处理!有关作品版权事宜请联系:+86-571-88970062

推荐资讯